# PANDIAN SARASWATHI YADAV ENGINEERING COLLEGE

(Approved by AICTE & Affiliated to Anna University, Chennai)

City Office: 10, Pandian Saraswathi St, Sivagami Nagar, Narayanapuram, Madurai - 625 014. Telefax- 0452 2682338, Mobile: 98423-02628

The number of research papers published per teacher during the academic year 2021 - 2022

| Sl.no | Title of paper                                   | Name of author/s  |

|-------|--------------------------------------------------|-------------------|

| 1.    | Application of TRIZ Concepts in Automobile Parts | Palanichamy R     |

|       | Production Industry: A Case Study                |                   |

| 2.    | Effect of Taguchi Counter Plot Function with     |                   |

|       | Process Window Approach Validation in the Sand   | Palanichamy R     |

|       | Casting Process                                  |                   |

| 3.    | A 2D Unified Suntheshold Drain Current           |                   |

|       | Investigation for Junction Less Cylindrical      | S.Manikandan      |

|       | Surrounding gate (JCSG) Silicon Nanowire         |                   |

|       | Transistors                                      |                   |

| 4.    | Deep Learning-Based Image Processing Approach    |                   |

|       | for Irradiance Estimation in MPPT Control of     | B Sakthivel       |

|       | Photovoltaic Applications                        |                   |

| 5.    | An Optimized Deep-Learning-Based Low Power       | B Sakthivel       |

|       | Approximate Multiplier Design                    |                   |

| 6.    | Artificial Neural Network Modeling of Abrasion   |                   |

|       | Loss and Surface Roughness of Crab Carapace      | S.Rajamuneeswaran |

|       | Impregnated Coir Vinyl Ester Composites          |                   |

# **Application of TRIZ Concepts in Automobile Parts Production Industry: A Case Study**

# Kumaravadivel A\*

Department of Mechanical Engineering College, Sir issac newton college of Engineering and Tech, Nagapattinam, Tamilnadu, India

# Kamatchi sankaran S, and Prabakaran T

Department of Mechanical Engineering-Meenakshi Sundararajan Engineering College, Kodampakkam Tamilnadu,India

## Palanichamy R

Department of Mechanical Engineering-Pandian Saraswathi Yadav Engineering

College, Sivagangai, Tamilnadu, India

Abstract: It is becoming increasingly difficult to ignore that cost reduction in product system are not supporting the development of innovation. This contradiction becomes a great challenge for any type of industry, to improve the competitive level. In this research, the focuses on the reducing defects in automobile parts thereby reduction of cost using TRIZ (Theory of Inventive Problem Solving) concepts. The TRIZ is applied in the gearbox assembly area with a view of improving quality of the assembling and ultimately to reduce the in process defects and consequent rejections. From the case studies, the results show that the magnitude of cost improvement and innovation achieved is more than the application of conventional tools. These change the limitation of mindset in cost reduction without compromise or trade-off, and open up new possibility of research for cost reduction in processes. TRIZ can be applied as a strategy tool in the real time company environment to reduce the huge production loss. TRIZ is a problem solving method based on logic and data, which accelerates the project team's ability to solve problems creatively. TRIZ also provides repeatability, predictability and reliability due to its structure and algorithmic approach. Hence the ultimate aim of the paper is to use TRIZ to reduce the loss or defects in gearbox assembly which contribute to huge loss of man power, time consumption & production cost is discussed.

**Keywords:** Automobile, defects reduction, gear box assembly, theory of innovative problem solving, TRIZ

Effect of Taguchi Counter Plot Function with Process Window Approach Validation in the Sand Casting Process

# S KAMATCHI SANKARAN<sup>1</sup>, T PRABAKARAN<sup>2</sup>, R PALANICHAMY<sup>3</sup>, \*A KUMARAVADIVEL<sup>4</sup>

<sup>1</sup>Assistant Professor, Department of Mechanical Engineering-Meenakshi Sundararajan Engineering College, Kodampakka Tamilnadu, India

<sup>3</sup>Professor, Department of Mechanical Engineering-Pandian Saraswathi Yadav Engineering College,Sivagangai, Tamilnadu,India

Abstract - This paper explains and illustrates the effect of the counterplot function with the Taguchi method to optimize the sand casting process operations using Process Window Approach (PWA) validation. The focus of this research is to minimize the defects in the sand casting process by analyzing the Taguchi method optimization with Process Window Approach. The Taguchi L27 orthogonal array (OA) with three-level is used for the study. The critical process parameters and the effect of counterplot interactions are analysed with the help of Taguchi's Method of experimental design. Subsequently, the significant parameters are determined by using ANOVA and the identified optimum levels of parameters are compared with PWA optimization validation to make the analysis more precise and cost cost-effective. The resultshows that the identified process parameters significantly control and reduce the defects and improve the efficiency of the cast iron flywheel manufacturing process. The confirmation experiments at the optimal levels identified using Taguchi with counter plot analysis and Process Window Approach validation shows that the identified parameters can be significantly improved to achieve more desirable results in minimizing defects.

Keywords; Taguchi, Sand casting process, Process window approach, validation, optimisation, Process capability, orthogonal array

# Introduction

The green sand mould casting is a predictable process with several process parameters contributing to the various Casting Quality features of the product. The quality of green sand in the mould is a significant phenomenon in which parameters are technically controllable or not technically controllable based on responding nature. A large number of experimental

<sup>&</sup>lt;sup>2</sup>Assistant Professor, Department of Mechanical Engineering-Meenakshi Sundararajan Engineering College, Kodampakka Tamilnadu, India

<sup>&</sup>lt;sup>4\*</sup>Professor, Department of Mechanical Engi<mark>neering College, S</mark>ir Issac Newton College of Engineering and Tech,Nagapattinam, Tamilnadu,India \*corresponding author

#### https://doi.org/10.100//312055-021-0

**ORIGINAL PAPER**

# A 2D Unified Subthreshold Drain Current Investigation for Junctionless Cylindrical Surrounding Gate(JCSG) Silicon Nanowire Transistor

S. Manıkandan 🄞 • P. Suveetha Dhanaselvam <sup>2</sup> • M. Karthigai Pandian <sup>3</sup>

Received: 16 June 2021 / Accepted: 21 July 2021 © Springer Nature B.V. 2021

#### Abstract

In this paper, an analytical model of transconductance, subthreshold current and transcapacitance for short-channel Junction Less Cylindrical Surrounding Gate Nanowire Transistor (JLCSGNWT) is derived. The 2D Poisson equation is solved by applying the boundary conditions and the physics-based model is derived for drain current in all three regions. The subthreshold drain current is further resolved to obtain transconductance and transcapacitance solution. The proposed model explicitly shows the effect of gate oxide thickness and silicon thickness variation on the subthreshold operation of the device to understand the performance of the device in a better way. The analytical model is verified by the TCAD simulator and offers further guidance for design under the 100 nm regime.

$\label{eq:continuous} \textbf{Keywords} \ \ \textbf{Junctionless}(JL) \cdot Cylindrical \ surrounding \ gate \ (CSG) \cdot Silicon \ nanowire \ (SiNW) \cdot Gate \ all \ around(GAA) \cdot Drain \ induced \ barrier \ lowering \ (DIBL) \cdot Short \ channel \ effects(SCE)$

## 1 Introduction

Due to the drastic reduction in device geometries, severe challenges are encountered during device fabrication [16]. The junction less transistor [6] demonstrates better control over the channel current than the traditional junction-based transistors [4, 7], because the current conduction is in the center of the channel not on the surface as other transistors. Nanowires have been used widely to fabricate surrounding gate field-effect transistors which offer zero trapped charges [5, 17].

S. Manikandan manisubbu07@gmail.com

> P. Suveetha Dhanaselvam suveethaj@gmail.com

M. Karthigai Pandian karthickpandian@gmail.com

Published online: 16 August 2021

- Department of ECE, Pandian Saraswathi Yaday Engineering College, Siyagangai, India

- Department of E.C., Velammal College of Engineering and Technology, Madurai, India

- Department of EECE, GITAM (Deemed to be university), Bangalore, India

Improvement of device performance with reduced Short Channel Effects (SCE) is investigated in detail with different gate geometries [14, 18, 22]. It is validated with cutting-edge simulators. Analytical models of short and long channel Junction Less(JL) Single Material(SM) Cylindrical Surrounding Gate(CSG) MOSFET was derived [1, 3, 12, 13, 21] and the parameters such as threshold voltage, subthreshold current, drain current is analyzed for all three regions of operations, trapped charges and different quantum effects. But analysis of small-signal characteristics of a device is still not explored. In Nanoscale dual material, tri material and gate all around(CSG) Transistor characteristics such as subthreshold behavior, SCE, transconductance and transcapacitane are also investigated [2, 9, 15, 19, 23, 24]. But an analytical model for transconductance and transcapacitance [8, 10, 11, 20] of SM JLCSG Silicon Nanowire (SiNW) is not investigated in detail to understand the small-signal behavior of the device. Hence a unified transconductance and transcapacitane model for SM JLCSG Si NW transistor is proposed. In this paper, the subthreshold model is developed for the first time to study the transconductance and transcapacitane for JLCSG SNW Transistor based on a closed-form solution of Poisson equation and current continuity equation, which is valid for subthreshold operation. The model explicitly shows how the

Springer

Original Article

# Deep Learning-Based Image Processing Approach for Irradiance Estimation in MPPT Control of Photovoltaic Applications

J. Shirisha<sup>1</sup>, C. P. Thamil Selvi<sup>2</sup>, S. Saru Priya<sup>2\*</sup>, V. Saravanan<sup>2\*</sup>, B. Sakthivel<sup>3\*</sup>, R. Surendiran<sup>3#</sup>

<sup>1</sup>Department of ECE, Malla Reddy Engineering College, Hyderabad.

<sup>2</sup>Department of CSE, PPG Institute of Technology, Coimbatore.

<sup>2\*</sup>Department of ECE, Velammal Engineering College, Chennai.

<sup>3\*</sup>Department of ECE, Pandian Saraswathi Yadav Engineering College, Sivagangai.

<sup>3\*</sup> School of Information Science, Annai College of Arts and Science, Kumbakonam, ORCID:0000-0003-1596-7874.

<sup>3#</sup>Corresponding Author: surendiranmca@gmail.com

Received: 19 July 2022 Revised: 09 September 2022 Accepted: 17 September 2022 Published: 30 September 2022

Abstract - Renewable energy contributes significantly to power generation to tackle the energy demand. Renewable energy is obtained from solar, wind, hydroelectric, etc. Among these, solar energy is considered the best suitable energy in terms of cleanliness and directly converts sunlight into electrical power by solar photovoltaic (PV) module. Solar panels' randomly changing power output due to irradiance is the biggest problem with solar panels. The concept of maximum power point tracking (MPPT) techniques is introduced to tackle this non-linear behavior of PV and optimize the PV system's efficiency. Various MPPT techniques have been proposed based on conventional and intelligent methods. In this work, a novel image processing-based MPPT technique is introduced to increase the efficiency of PV. The irradiance level is accurately classified using the self-learned EfficientNetB0 deep learning model. The parameters of the EfficientNetB0 model are adjusted using Tuna Swarm Optimization. Results show that the tracking efficiency is higher than other intelligent MPPT techniques. Also, the classification accuracy of the proposed learning model is superior to conventional models.

Keywords - MPPT, PV and EfficientNetB0.

## 1. Introduction

PV systems are cost-effective renewable energy sources used to reduce global warming and reduce the necessity of fossil fuels. The effectiveness of PV is a good alternative to avoid environmental pollution and reduce CO2 emissions. The efficiency of a PV system is greatly affected by the seasonal climate conditions and the non-linear behavior of solar irradiance. The concept of MPPT is used to overcome these issues and improve the PV system's efficiency under partial shading conditions.

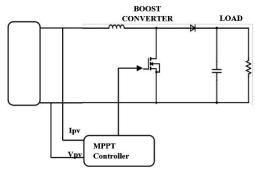

The general block of PV-based power generation is shown in Fig 1. The solar-based power system consists of a PV array, DC-DC converter and MPPT controller. The major function of the MPPT controller is to generate a duty cycle for the DC-DC converter by measuring PV output voltage and current. The maximum power is achieved by the suitable adjustment of duty cycles, which control the charging and discharging of the inductor and capacitors in the converter.

Fig. 1 The elements of solar power generation.

Generally, the MPPT techniques are classified into two categories: non-uniform irradiance and uniform radiance. The well-known non-uniform irradiance MPPT technique is Perturb and Observe (P&O) Method, Incremental Conductance (INC) Method, Hill Climbing (HC) Method and Current Sweep (CS) Method etc. the uniform irradiance MPPT technique uses artificial intelligence to achieve

# An Optimized Deep-Learning-Based Low Power Approximate Multiplier Design

M. Usharani<sup>1,\*</sup>, <mark>B. Sakthivel²</mark>, S. Gayathri Priya³, T. Nagalakshmi⁴ and J. Shirisha<sup>5</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Er.Perunal Manimekalai College of Engineering, Konneripalli, Hosur, 635117, India

<sup>2</sup>Department of Electronics and Communication Engineering, Pandian Saraswathi Yadav Engineering College, Sivagangai, Tamilnadu, 630561, India

Received: 24 January 2022; Accepted: 27 February 2022

Abstract: Approximate computing is a popular field for low power consumption that is used in several applications like image processing, video processing, multimedia and data mining. This Approximate computing is majorly performed with an arithmetic circuit particular with a multiplier. The multiplier is the most essential element used for approximate computing where the power consumption is majorly based on its performance. There are several researchers are worked on the approximate multiplier for power reduction for a few decades, but the design of low power approximate multiplier is not so easy. This seems a bigger challenge for digital industries to design an approximate multiplier with low power and minimum error rate with higher accuracy. To overcome these issues, the digital circuits are applied to the Deep Learning (DL) approaches for higher accuracy. In recent times, DL is the method that is used for higher learning and prediction accuracy in several fields. Therefore, the Long Short-Term Memory (LSTM) is a popular time series DL method is used in this work for approximate computing. To provide an optimal solution, the LSTM is combined with a meta-heuristics Jellyfish search optimisation technique to design an input aware deep learning-based approximate multiplier (DLAM). In this work, the jelly optimised LSTM model is used to enhance the error metrics performance of the Approximate multiplier. The optimal hyperparameters of the LSTM model are identified by jelly search optimisation. This fine-tuning is used to obtain an optimal solution to perform an LSTM with higher accuracy. The proposed pre-trained LSTM model is used to generate approximate design libraries for the different truncation levels as a function of area, delay, power and error metrics. The experimental results on an 8-bit multiplier with an image processing application shows that the proposed approximate computing multiplier achieved a superior area and power reduction with very good results on error rates.

Keywords: Deep learning; approximate multiplier; LSTM; jellyfish

This work is licensed under a Creative Commons Attribution 4.0 International License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

<sup>&</sup>lt;sup>3</sup>Department of Electronics and Communication Engineering, R.M.D Engineering College, Gummidipundi, Tamilnadu, 601206, India <sup>4</sup>Department of Computer Science and Engineering, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, 522502, India

<sup>&</sup>lt;sup>5</sup>Department of Electronics and Communication Engineering, Malla Reddy Engineering College, Hyderabad, Telangana, 500015, India \*Corresponding Author: M. Usharani. Email: usharaniphd@gmail.com